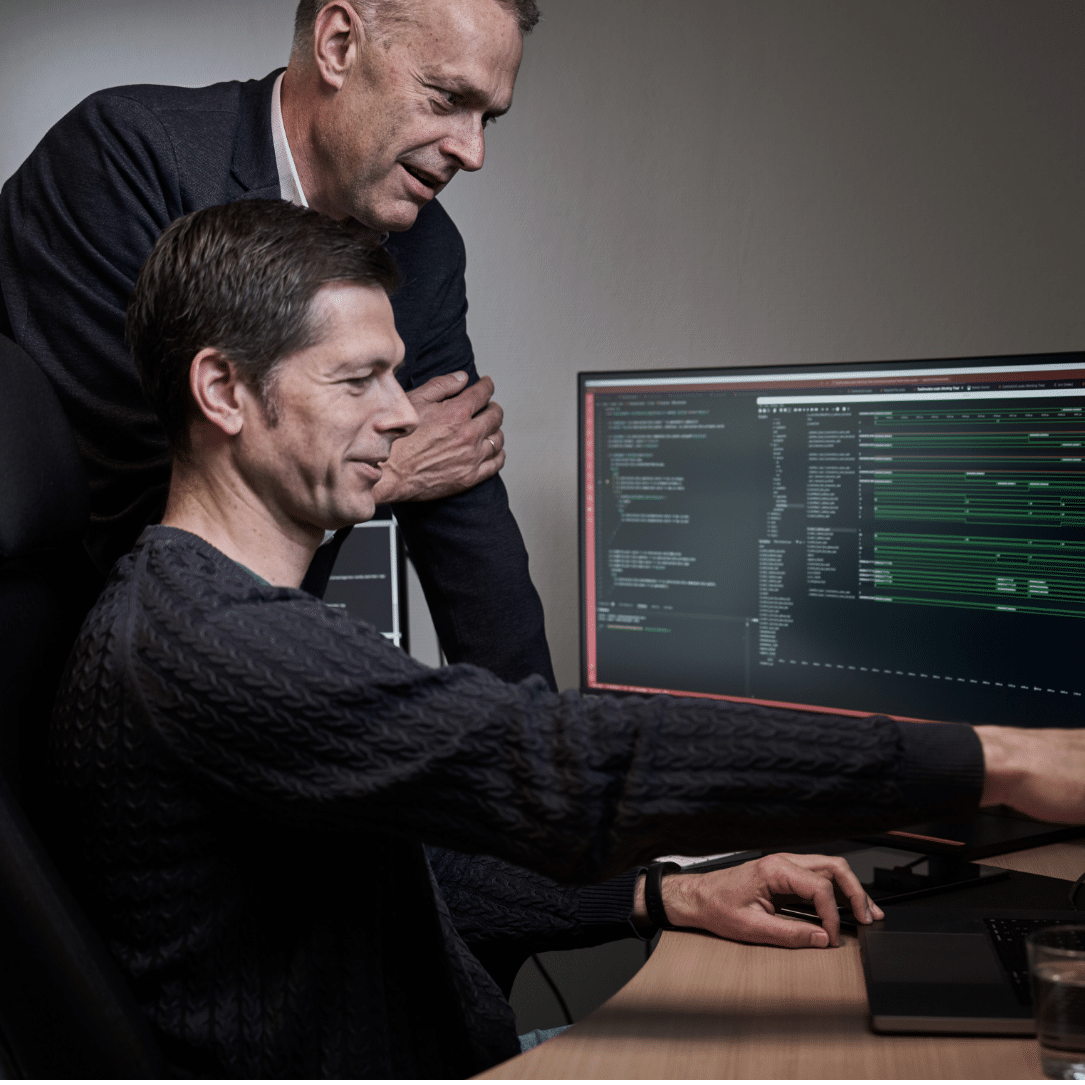

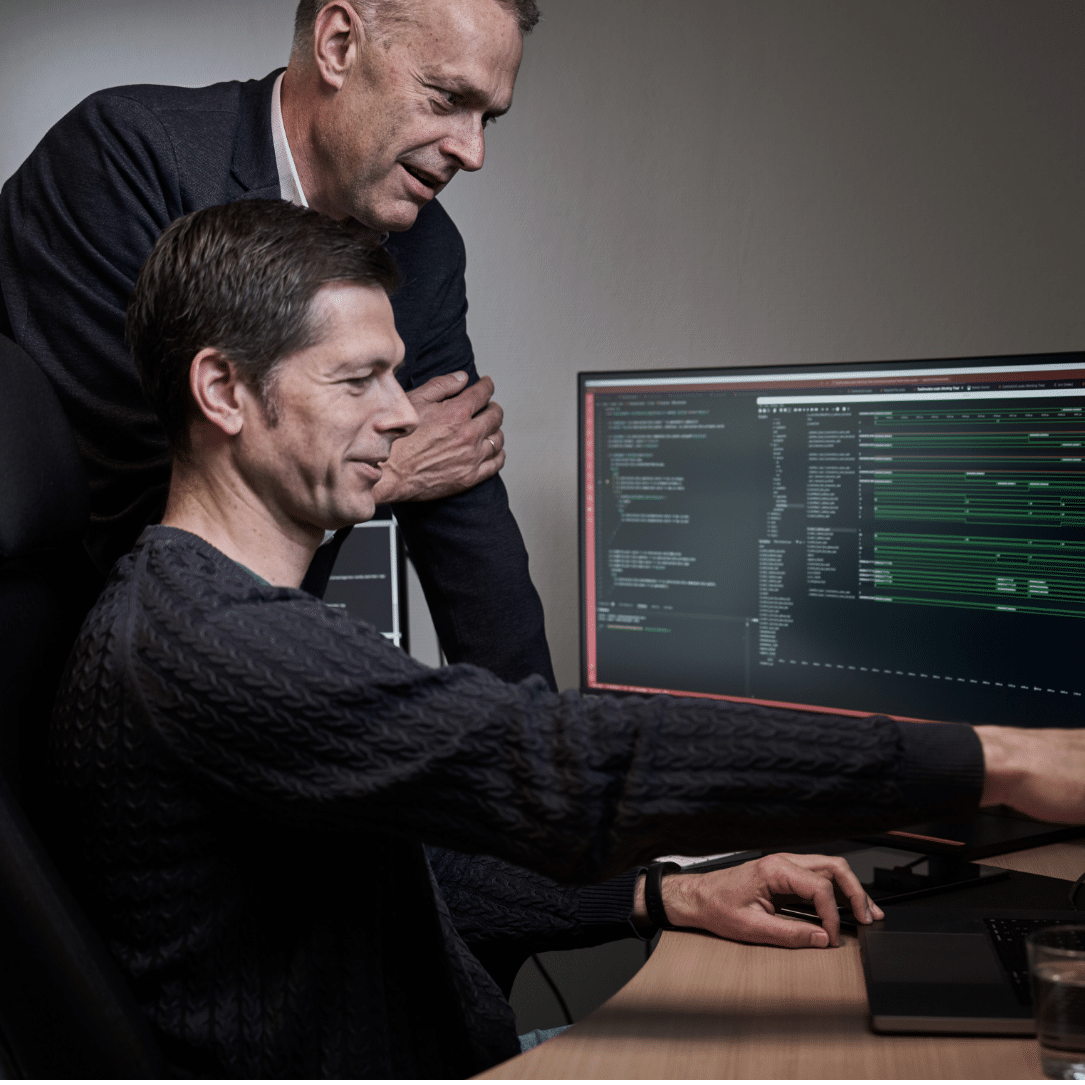

Introducing the New Compute Paradigm: The General-Purpose Accelerator

Ascenium revolutionizes compute performance with its General-Purpose Accelerator (GPA). While current GPU technology accelerates AI software, Ascenium’s innovation extends to all generic software, already delivering up to 4x performance replacing state-of-the-art CPUs.

The problem

The consumption of energy by data centers currently accounts for 2% of world’s total, and it is fast-growing. Current CPU technology has reached technical limitations, and challenges with high energy costs and CO2 emissions remain unresolved.

The solution

Ascenium has designed a General Purpose Accelerator with up to 4x efficiency improvement for data-center workloads, allow management and control of performance, energy cost and carbon footprint.

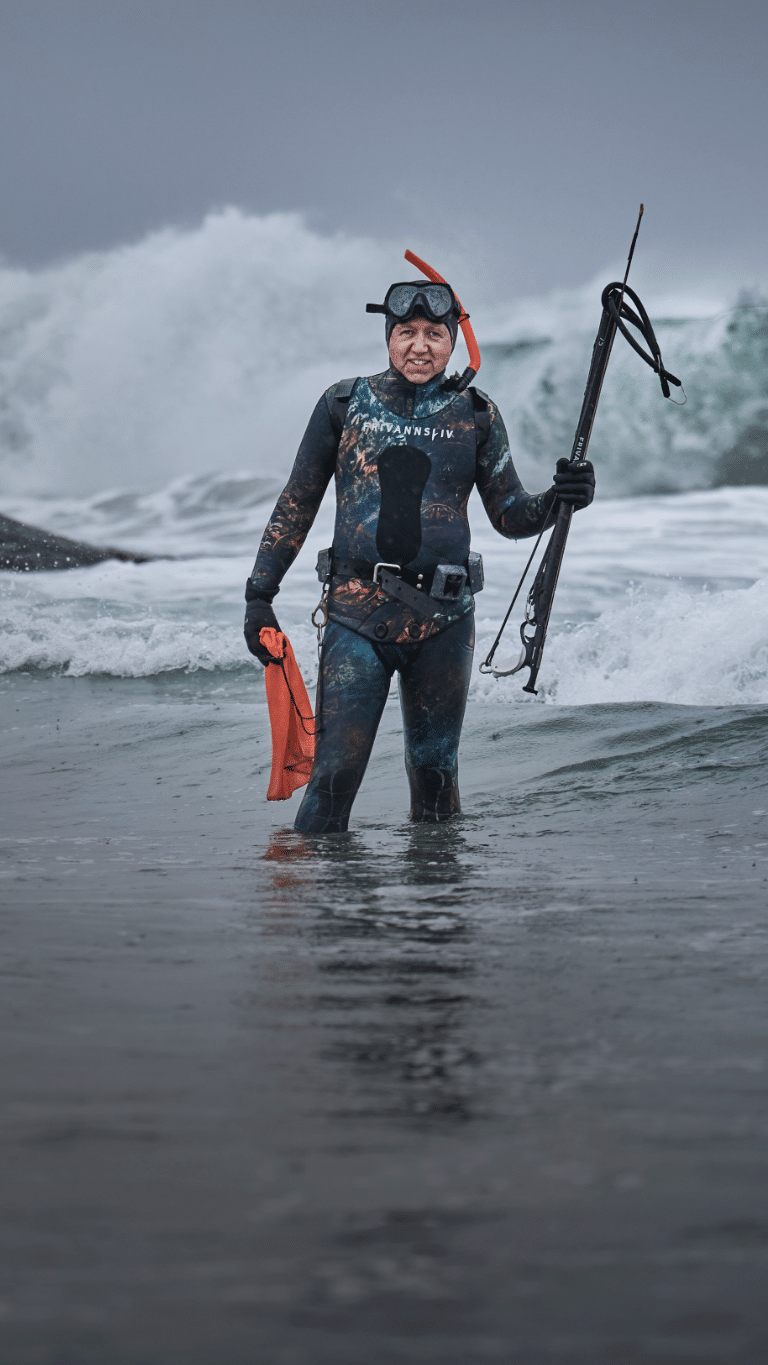

Join the team

Ascenium is looking for experienced team members with the skillset to build a high-performance state-of-the-art microprocessor. Up for the challenge?